Subtotal: රු451.00

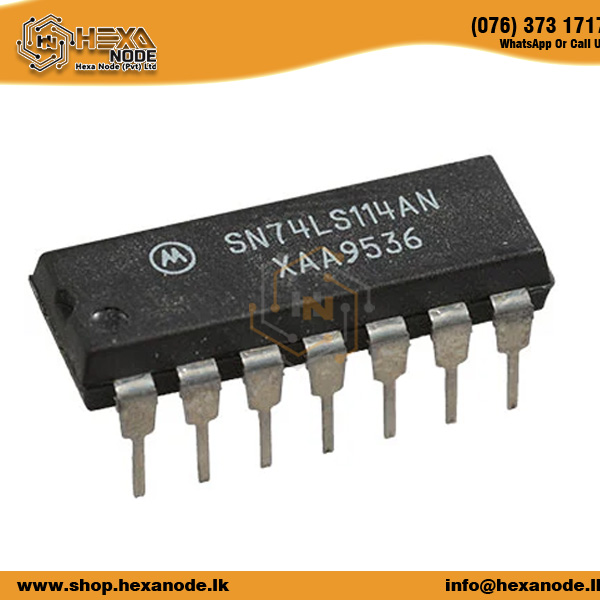

74LS114 DIP Dual J-K Negative-Edge-Triggered Flip-Flops

10 in stock

The 74LS114 is a dual J-K negative-edge-triggered flip-flop in a DIP-14 package, offering versatile synchronous switching, manual reset/set, and low power operation for digital systems. It is ideal for counters, registers, and timing circuits that require high-speed state memory and control.

රු160.00

10 in stock

Product Description: 74114 DIP Dual J-K Negative-Edge-Triggered Flip-Flops

The 74114 is a dual J-K negative-edge-triggered flip-flop integrated circuit in a DIP package, designed for robust data storage and control in digital applications. This versatile device features two J-K flip-flops with preset functionality, a common clear, and a common clock input, allowing for synchronized operation and flexible design in sequential logic circuits. The negative-edge triggering enhances performance in high-speed applications, making it ideal for various digital systems.

Key Features:

- Dual J-K flip-flops with negative-edge triggering for reliable operation

- Preset function for flexible data handling

- Common clear and clock inputs for synchronized control

- DIP packaging for easy integration into breadboards and circuit boards

Applications:

- Digital counters and registers

- State machines and sequence generators

- Data storage and retrieval in digital circuits

- General-purpose flip-flop applications in electronic systems

Package Includes:

- 1 x 74114 DIP Dual J-K Negative-Edge-Triggered Flip-Flops (with Preset, Common Clear, and Common Clock)

Please note that the product image is for illustrative purposes only. The actual product may vary slightly in appearance.

Based on 0 reviews

Be the first to review “74LS114 DIP Dual J-K Negative-Edge-Triggered Flip-Flops” Cancel reply

Related products

-

ICs, Memory ICs, Semiconductors, Special Purpose ICs

AT93C46 DIP 1KBit I2C-Compatible, (2-Wire) Serial EEPROM 5.5V 2.0mA

ICs, Memory ICs, Semiconductors, Special Purpose ICs

ICs, Memory ICs, Semiconductors, Special Purpose ICsAT93C46 DIP 1KBit I2C-Compatible, (2-Wire) Serial EEPROM 5.5V 2.0mA

0 out of 5(0)The AT93C46 DIP 5.5V 2MA 3-Wire Serial EEPROM provides reliable non-volatile memory storage, low power consumption, and easy integration for various electronic applications.

SKU: 3000468 -

ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICs

TNY274GN SOP – SMPS TINY Switch-II Off-Line Switcher IC

ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICs

ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICsTNY274GN SOP – SMPS TINY Switch-II Off-Line Switcher IC

0 out of 5(0)The TNY274GN is a compact off-line switcher IC for SMPS applications, featuring high efficiency, low standby power, and integrated protection in a SOP-7 package.

SKU: 3000435 -

ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICs

TNY254GN SOP / SMD SMPS TINY Switch-II Off-Line Switcher IC

ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICs

ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICsTNY254GN SOP / SMD SMPS TINY Switch-II Off-Line Switcher IC

0 out of 5(0)The TNY254GN SOP – SMPS TINY Switch-II Off-Line Switcher IC offers efficient power conversion with built-in protections, making it ideal for compact power supply applications.

SKU: 3000467 -

Audio Devices, General Purpose ICs, ICs, Operational Amplifier ICs, Other Audio Modules, Semiconductors, Special Purpose ICs

LM386 SOP – Low Voltage Audio Amplifier IC

Audio Devices, General Purpose ICs, ICs, Operational Amplifier ICs, Other Audio Modules, Semiconductors, Special Purpose ICs

Audio Devices, General Purpose ICs, ICs, Operational Amplifier ICs, Other Audio Modules, Semiconductors, Special Purpose ICsLM386 SOP – Low Voltage Audio Amplifier IC

0 out of 5(0)The LM386 SOP Low Voltage Audio Amplifier IC operates from 4V to 12V, providing efficient audio amplification with low distortion, ideal for portable devices and projects.

SKU: 3000417

PC817 SMD / SOP Optocoupler

PC817 SMD / SOP Optocoupler  TL082CP DIP -18V 200mA Dual Operational Amplifiers

TL082CP DIP -18V 200mA Dual Operational Amplifiers  FQA19N60 /19N60 600V N-Channel TO-3PIN MOSFET

FQA19N60 /19N60 600V N-Channel TO-3PIN MOSFET

There are no reviews yet.