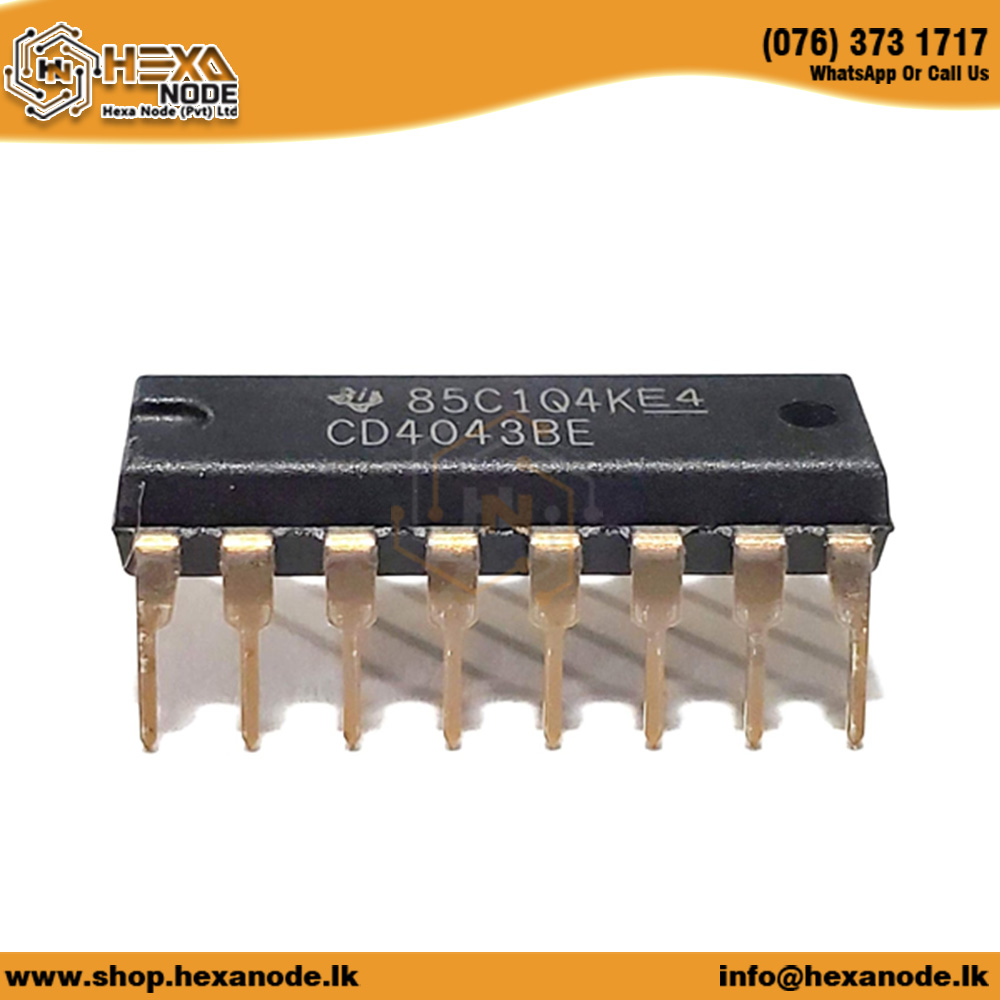

CD4043 DIP CMOS Quad 3-State R-S Latch

11 in stock

The CD4043 DIP CMOS Quad 3-State R-S Latch contains four independent R-S latches with 3-state outputs for flexible control in bus systems and digital circuits. Ideal for data latching, signal routing, and control systems, the IC operates over a voltage range of 3V to 18V, offering low power consumption and high noise immunity.

රු215.00

11 in stock

Product Description: CD4043 DIP CMOS Quad 3-State R-S Latch

The CD4043 DIP CMOS Quad 3-State R-S Latch is a CMOS-based logic device that contains four independent R-S (Reset-Set) latches with 3-state outputs. Each latch in the IC is a basic storage element that can be set (1) or reset (0) based on the input signals. The 3-state output allows each latch to be independently disabled, providing high flexibility for bus systems or situations where multiple outputs need to be managed without interference.

The R-S latch is a basic form of memory that holds a binary value (0 or 1) and can be toggled or reset using its control inputs. The 3-state capability provides three possible output states: high, low, and high impedance (Z), allowing for tri-state logic or bus systems where multiple devices can share the same data lines without interfering with each other.

The CMOS technology ensures low power consumption, high noise immunity, and fast switching speeds, making the CD4043 suitable for both digital logic systems and communication circuits where efficient and reliable control of outputs is needed. The DIP (Dual In-line Package) format ensures ease of integration into both through-hole PCBs and breadboard prototypes.

Key Features:

- Quad 3-State R-S Latches: The IC contains four independent R-S latches, each with 3-state outputs for flexible control in bus and data-line systems.

- 3-State Outputs: Each latch provides a high, low, or high impedance (Z) output, making it ideal for bus systems and applications where multiple devices need to share data lines.

- Reset and Set Functionality: The R-S latches allow for Set (S) and Reset (R) control inputs, enabling easy binary storage and toggling.

- CMOS Technology: Built using CMOS (Complementary Metal-Oxide-Semiconductor) technology, which provides low power consumption, high noise immunity, and reliable performance.

- Wide Voltage Range: The CD4043 operates within a voltage range of 3V to 18V, allowing it to be integrated into a variety of circuit designs.

- DIP Package: The IC is provided in a DIP (Dual In-line Package), ideal for through-hole PCB designs or breadboard prototyping.

- Flexible Control: The 3-state capability allows each latch to be independently controlled, making it ideal for use in systems that need to manage multiple outputs without interference.

- Reliable Storage: The R-S latch is a simple but reliable form of memory, used widely in state machines, data latching, and control circuits.

Applications:

- Bus Systems: The 3-state outputs make the CD4043 ideal for bus systems, where multiple devices share a common data line and need to enable or disable their outputs without conflict.

- Data Latching: The IC can be used in data latching applications, where it is necessary to store a binary value temporarily for later use, such as in shift registers or data buffers.

- Control Circuits: Used in control systems for logic storage or to store state information, especially in state machines and sequencers.

- Digital Logic Systems: The CD4043 is commonly used in digital logic circuits where latching and output control are needed, such as in timing and sequencing applications.

- Memory and Storage: Can be used as a simple form of volatile memory for storing states or controlling devices in embedded systems and microcontroller circuits.

- Signal Routing: The 3-state functionality makes the CD4043 useful in signal routing and multiplexing circuits, where the output must be selectively enabled or disabled based on control signals.

- Communication Systems: Used in communication circuits to manage signal flow, where multiple devices need to share the same data lines without interfering with each other.

- Multiplexing Applications: Can be used in multiplexing systems where multiple signals need to be sent over a common bus or data line, with each latch controlled independently.

Package Included:

1 x CD4043 DIP CMOS Quad 3-State R-S Latch

Please note that the product image is for illustrative purposes only. The actual product may vary slightly in appearance.

Based on 0 reviews

Be the first to review “CD4043 DIP CMOS Quad 3-State R-S Latch” Cancel reply

Related products

-

74XX Series, General Purpose ICs, ICs, Semiconductors, Special Purpose ICs

74HC32 SOP Quad 2-Input NOR Gate

74XX Series, General Purpose ICs, ICs, Semiconductors, Special Purpose ICs

74XX Series, General Purpose ICs, ICs, Semiconductors, Special Purpose ICs74HC32 SOP Quad 2-Input NOR Gate

0 out of 5(0)The 74HC32 is a quad 2-input NOR gate IC in an SOP-14 package, designed for low power and high-speed performance. It is ideal for use in digital logic circuits, control systems, and signal processing applications, offering reliable operation with four independent NOR gates.

SKU: 3000527 -

IGBT, Semiconductors, Transistors

SGP30N60HS / 30N60 TO-220 600V 30A High Speed IGBT

0 out of 5(0)The 30N60 is a high-voltage, high Speed IGBT designed for efficient power switching applications. It offers a balance of high voltage capability, moderate current handling, and fast switching speed.

SKU: 2000513 -

Battery & Power, Battery Chargers, BMS Modules, ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICs

TP4056E 3V-7V 1A Lithium Battery Charger IC

Battery & Power, Battery Chargers, BMS Modules, ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICs

Battery & Power, Battery Chargers, BMS Modules, ICs, Semiconductors, Special Purpose ICs, Voltage Regulator ICsTP4056E 3V-7V 1A Lithium Battery Charger IC

0 out of 5(0)The TP4056E is a Li-ion battery charger IC, operating from 3V to 7V with 1A charging current, ideal for portable electronics and battery management systems.

SKU: 3000421 -

General Purpose ICs, ICs, Operational Amplifier ICs, Semiconductors

TL082C SOP / SMD 15V Dual Operational Amplifiers

General Purpose ICs, ICs, Operational Amplifier ICs, Semiconductors

General Purpose ICs, ICs, Operational Amplifier ICs, SemiconductorsTL082C SOP / SMD 15V Dual Operational Amplifiers

0 out of 5(0)The TL082C SOP 15V Dual Operational Amplifiers provide high-performance, low-noise amplification in a compact package, ideal for audio, signal conditioning, and data acquisition applications.

SKU: 3000472

There are no reviews yet.